AN10677 Reset of the TDA8007B using delay pin Rev. 1.0 — 9 June 2011

**Application note**

#### **Document information**

| Info     | Content                                                                                         |

|----------|-------------------------------------------------------------------------------------------------|

| Keywords | TDA8007B, Software reset, Delay pin                                                             |

| Abstract | This addendum describes how to do a complete reset of the TDA8007B chip without a power on/off. |

|          | The reset can be executed by a microcontroller using pin Delay (#48).                           |

#### Reset of the TDA8007B using delay pin

#### **Revision history**

| Rev | Date     | Description   |

|-----|----------|---------------|

| 1.0 | 20110609 | First version |

### **Contact information**

For more information, please visit: <u>http://www.nxp.com</u>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

AN10677

All information provided in this document is subject to legal disclaimers.

### 1. Introduction

The TDA8007B doesn't have an external dedicated reset pin. Therefore the chip cannot be completely reset unless with a hard Power ON/Power OFF.

This functionality can be achieved using another specificity of the TDA8007B: the delay pin.

This application note is an addendum to the TDA8007B generic application note AN01054.

### 2. Presentation

### 2.1 General use

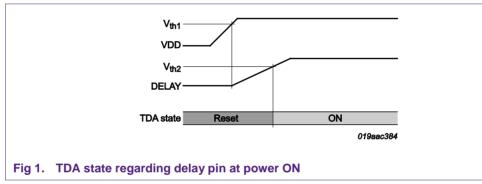

The delay pin is used by TDA8007B to maintain the chip in reset state for a chosen delay when the power supply is applied to the IC.

### 2.2 Internal structure

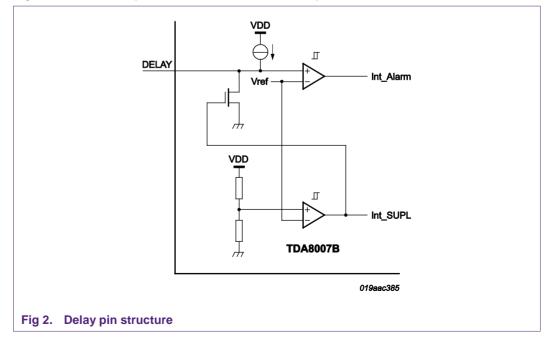

Fig. 2 shows the simplified internal structure of this pin

Int\_Alarm is an internal signal which resets the TDA: proper card deactivation followed by a complete digital reset.

Int\_SUPL is the internal signal which will set the SUPL bit (HSR #4), what generates an interrupt.

As seen in this structure, a reset using pin Delay will have exactly the same action as a power OFF, except for the interrupt generation.

### 3. Software reset implementation

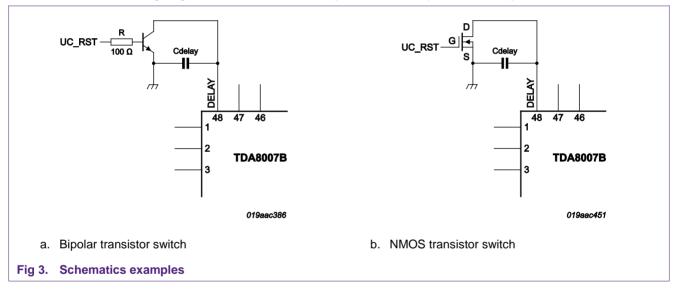

Regarding the pin structure, the delay pin can be used externally as a reset pin.

In general use, this pin must be left open (only connected to the Cdelay capacitor)

When reset is wanted, the microcontroller must drive this pin to GND.

Fig. 3 gives two schematic examples to use this pin as a reset pin

During general use, UC\_RST command must be LOW to keep the switch open. When a reset is needed, drive UC\_RST HIGH to have the switch closed. Then the delay pin is connected to the ground and a complete chip reset is performed.

When UC\_RST is released (driven LOW), delay pin will increase in the same way as after a power ON.

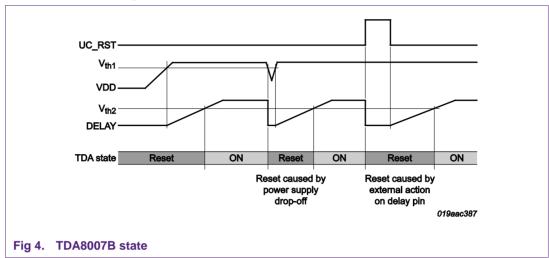

Fig. 4 shows the TDA8007B state with action on the power supply supervisor or the external reset management.

**Application note**

### Reset of the TDA8007B using delay pin

AN10677

### 4. Legal information

#### 4.1 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 4.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

**Right to make changes** — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

### 4.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

Application note

### Reset of the TDA8007B using delay pin

## 5. List of figures

| Fig 1. | TDA state regarding delay pin at power ON | 3 |

|--------|-------------------------------------------|---|

| Fig 2. | Delay pin structure                       | 3 |

| Fig 3. | Schematics examples                       | 4 |

| Fig 4. | TDA8007B state                            | 5 |

**Application note**

#### Reset of the TDA8007B using delay pin

### 6. Contents

| 1.  | Introduction                  | 3 |

|-----|-------------------------------|---|

| 2.  | Presentation                  | 3 |

| 2.1 | General use                   | 3 |

| 2.2 | Internal structure            | 3 |

| 3.  | Software reset implementation | 4 |

| 4.  | Legal information             | 6 |

| 4.1 | Definitions                   | 6 |

| 4.2 | Disclaimers                   | 6 |

| 4.3 | Trademarks                    | 6 |

| 5.  | List of figures               | 7 |

| 6.  | Contents                      | 8 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP B.V. 2011.

#### All rights reserved.

For more information, visit: http://www.nxp.com For sales office addresses, please send an email to: salesaddresses@nxp.com

> Date of release: 9 June 2011 Document identifier: AN10677